COMPLIANT

GREEN

(5-2008)

## Vishay Semiconductors

## 2-Line BUS-Port ESD-Protection - Flow Through Design

### **MARKING** (example only)

Dot = pin 1 marking

Y = type code (see table below)

XX = date code

#### **FEATURES**

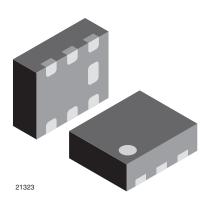

- Compact LLP1713-7L package

- Low package height < 0.6 mm

- 2-line ESD-protection

- Low leakage current I<sub>R</sub> < 0.1 μA</li>

- Low load capacitance C<sub>D</sub> = 0.8 pF

- Ideal for high speed data line like

- HDMI, DisplayPort, eSATA

- USB, 1394/firewire

- ESD-protection acc. IEC 61000-4-2

- ± 15 kV contact discharge

- ± 15 kV air discharge

- Soldering can be checked by standard vision inspection. No X-ray necessary

- e4 precious metal (e.g. Ag, Au, NiPd, NiPdAu) (no Sn)

- Compliant to RoHS directive 2002/95/EC and in accordance to WEEE 2002/96/EC

| ORDERING INFORMATION      |                    |                                                |                        |  |  |

|---------------------------|--------------------|------------------------------------------------|------------------------|--|--|

| DEVICE NAME ORDERING CODE |                    | TAPED UNITS PER REEL<br>(8 mm TAPE ON 7" REEL) | MINIMUM ORDER QUANTITY |  |  |

| VBUS052CD-FAH             | VBUS052CD-FAH-GS08 | 3000                                           | 15 000                 |  |  |

| PACKAGE DATA  |                 |              |        |                                      |                                      |                          |

|---------------|-----------------|--------------|--------|--------------------------------------|--------------------------------------|--------------------------|

| DEVICE NAME   | PACKAGE<br>NAME | TYPE<br>CODE | WEIGHT | MOLDING COMPOUND FLAMMABILITY RATING | MOISTURE<br>SENSITIVITY LEVEL        | SOLDERING<br>CONDITIONS  |

| VBUS052CD-FAH | LLP1713-7L      | G            | 3.7 mg | UL 94 V-0                            | MSL level 1<br>(according J-STD-020) | 260 °C/10 s at terminals |

| ABSOLUTE MAXIMUM RATINGS |                                                           |                  |               |      |  |  |

|--------------------------|-----------------------------------------------------------|------------------|---------------|------|--|--|

| PARAMETER                | TEST CONDITIONS                                           | SYMBOL           | VALUE         | UNIT |  |  |

| Peak pulse current       | Acc. IEC 61000-4-5; t <sub>P</sub> = 8/20 μs; single shot | I <sub>PPM</sub> | 3.5           | Α    |  |  |

| Peak pulse power         | Acc. IEC 61000-4-5; t <sub>P</sub> = 8/20 μs; single shot | P <sub>PP</sub>  | 63            | W    |  |  |

| ESD immunity             | Contact discharge acc. IEC 61000-4-2; 10 pulses           | V <sub>ESD</sub> | ± 15          | kV   |  |  |

|                          | Air discharge acc. IEC 61000-4-2; 10 pulses               | V <sub>ESD</sub> | ± 15          | kV   |  |  |

| Operating temperature    | Junction temperature                                      | TJ               | - 40 to + 125 | °C   |  |  |

| Storage temperature      |                                                           | T <sub>STG</sub> | - 55 to + 150 | °C   |  |  |

<sup>\*\*</sup> Please see document "Vishay Material Category Policy": www.vishay.com/doc?99902

# Vishay Semiconductors 2-Line BUS-Port ESD-Protection - Flow Through Design

| ELECTRICAL CHARACTERISTICS VBUS052CD-FAH (pin 1 or 2 to pin 3) |                                                |                    |      |        |      |       |  |

|----------------------------------------------------------------|------------------------------------------------|--------------------|------|--------|------|-------|--|

| PARAMETER                                                      | TEST CONDITIONS/REMARKS                        | SYMBOL             | MIN. | TYP.   | MAX. | UNIT  |  |

| Protection paths                                               | Number of line which can be protected          | N <sub>lines</sub> | -    | -      | 2    | lines |  |

| Reverse working voltage                                        | at I <sub>R</sub> = 0.1 μA                     | V <sub>RWM</sub>   | 5    | -      | -    | V     |  |

| Reverse current                                                | at $V_R = V_{RWM} = 5 \text{ V}$               | I <sub>R</sub>     | -    | < 0.01 | 0.1  | μΑ    |  |

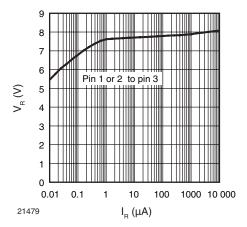

| Reverse breakdown voltage                                      | at I <sub>R</sub> = 1 mA                       | $V_{BR}$           | 6.9  | 7.9    | 8.7  | V     |  |

| Clamping voltage                                               | at I <sub>PP</sub> = 1 A; acc. IEC 61000-4-5   | V <sub>C</sub>     | -    | 10     | 12   | V     |  |

|                                                                | at I <sub>PP</sub> = 3.5 A; acc. IEC 61000-4-5 | V <sub>C</sub>     | -    | 15     | 18   | V     |  |

| Forward clamping voltage                                       | at I <sub>F</sub> = 1 A; acc. IEC 61000-4-5    | V <sub>F</sub>     | -    | 1.9    | 2.4  | V     |  |

|                                                                | at I <sub>F</sub> = 3.5 A; acc. IEC 61000-4-5  | V <sub>F</sub>     | -    | 4      | 5    | V     |  |

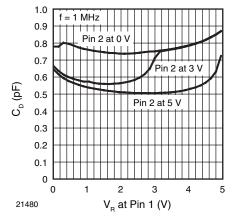

| Line capacitance                                               | at $V_R = 0 V$ ; $f = 1 MHz$                   | C <sub>D</sub>     | -    | 0.8    | 1    | pF    |  |

#### Note

• Ratings at 25 °C, ambient temperature unless otherwise specified

#### **APPLICATION NOTE**

The **VBUS052CD-FAH** is a two-line ESD-protection device with the characteristic of a Z-diode with a high ESD immunity and a very low capacitance which makes it usable for high frequency applications like USB2.0 or HDMI.

With the **VBUS052CD-FAH** two high speed data lines can be protected against transient voltage signals like ESD (Electro Static Discharge). Connected to the data line (pin 1 and pin 2) and to ground (pin 3) negative transients will be clamped close below the ground level while positive transients will be clamped close above the 5 V working range. The clamping behaviour of the **VBUS052CD-FAH** is bidirectional but asymmetrical (**BiAs**) and so it offers the best protection for applications running up to 5 V.

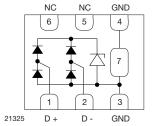

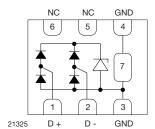

Pin configuration:

- Pin 3, 4 and 7 are internally shorted and have to be connected to ground

- Pin 1 and 2 are the inputs for the data lines D+ and D-

- Pin 5 and 6 are not connected internally

#### **FLOW THROUGH DESIGN**

Modern digital transmission lines can be clocked up to 480 Mbit/s (USB2.0) or 1.65 Gbit/s (HDMI).

At such high data rates the transmission lines like cables or the line traces on the PCBs have to be very homogeneous regarding their surge impedance. This requires well defined trace dimensions as trace width and distance which have to be calculated depending on the requested surge impedance (e.g.  $50~\Omega$ ) and the PCB material and layer dimensions. Any device connected to the data lines - like ESD-protection devices - have to be connected with minimal changes in these trace dimensions and distances.

With the package in the so called "Flow Through Design" this is possible. The lines are running straight along the PCB while the **VBUS052CD-FAH** is placed on top without any vias or loops.

# 2-Line BUS-Port ESD-Protection - Vishay Semiconductors Flow Through Design

### **TYPICAL CHARACTERISTICS** (T<sub>amb</sub> = 25 °C, unless otherwise specified)

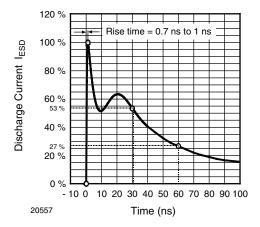

Fig. 1 - ESD Discharge Current Wave Form acc. IEC 61000-4-2 (330  $\Omega/150$  pF)

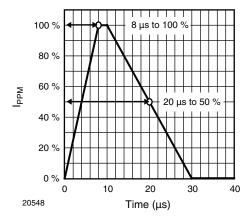

Fig. 2 - 8/20 µs Peak Pulse Current Wave Form acc. IEC 61000-4-5

Fig. 3 - Typical Capacitance  $C_D$  vs. Reverse Voltage  $V_R$

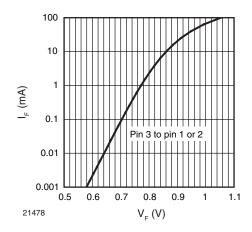

Fig. 4 - Typical Forward Current  $I_{\text{F}}$  vs. Forward Voltage  $V_{\text{F}}$

Fig. 5 - Typical Reverse Voltage  $V_R$  vs. Reverse Current  $I_R$

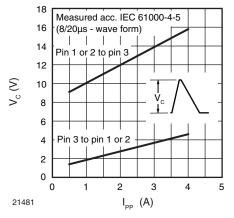

Fig. 6 - Typical Peak Clamping Voltage  $V_{C}$  vs. Peak Pulse Current  $I_{PP}$

# Vishay Semiconductors 2-Line BUS-Port ESD-Protection - Flow Through Design

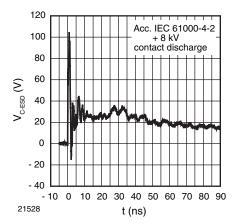

Fig. 7 - Typical Clamping Performance at + 8 kV Contact Discharge (acc. IEC 61000-4-2)

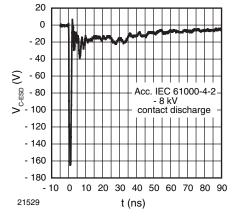

Fig. 8 - Typical Clamping Performance at - 8 kV Contact Discharge (acc. IEC 61000-4-2)

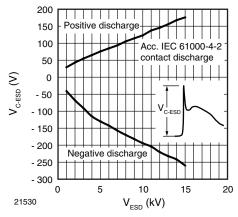

Fig. 9 - Typical Peak Clamping Voltage at ESD Contact Discharge (acc. IEC 61000-4-2)

# 2-Line BUS-Port ESD-Protection - Vishay Semiconductors Flow Through Design

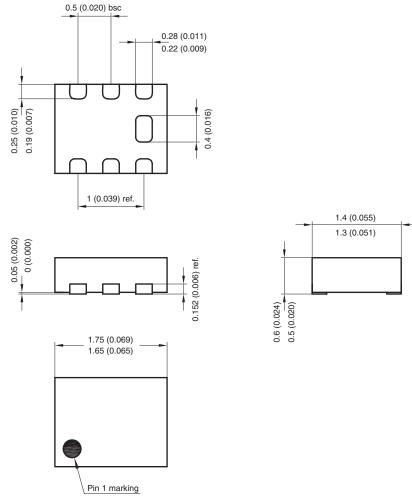

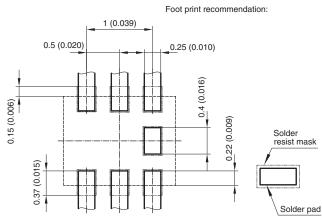

### PACKAGE DIMENSIONS in millimeters (inches): LLP1713-7L

Document no.:S8-V-3906.04-008 (4) Created - Date: 15. April 2008 Rev. 2 - Date: 09. Sep. 2008

21329

Vishay

### **Disclaimer**

All product specifications and data are subject to change without notice.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained herein or in any other disclosure relating to any product.

Vishay disclaims any and all liability arising out of the use or application of any product described herein or of any information provided herein to the maximum extent permitted by law. The product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein, which apply to these products.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay.

The products shown herein are not designed for use in medical, life-saving, or life-sustaining applications unless otherwise expressly indicated. Customers using or selling Vishay products not expressly indicated for use in such applications do so entirely at their own risk and agree to fully indemnify Vishay for any damages arising or resulting from such use or sale. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

Product names and markings noted herein may be trademarks of their respective owners.

Revision: 18-Jul-08

Document Number: 91000 www.vishay.com